# THE MULTI-COMPONENT IC PACKAGING MARKET

# 2014 EDITION

A Strategic Report on the Growing Markets for Multi-Component IC Packaging Technologies

# **Report Coverage**

- Stacked Packages

- Through Silicon Vias (TSV)

- 2.5-D and 3-D Integration

- 2.5-D Interposers

- System in Package (SiP)

# **Report Highlights**

- Market Analysis and Forecasts, 2011-2017

- Key Application Forecasts

- New Product/Technology

Introductions

- 32 Tables, 65 Figures

#### **New Venture Research**

337 Clay St., Suite 101 Nevada City, CA 95959 Tel: (530) 265-2004 A Technology Market Research Company

info@newventureresearch.com www.newventureresearch.com

Fax: (530) 265-1998

# The Multi-Component IC Packaging Market, 2014 Edition

# **Synopsis**

Complex multi-component packages have added a new dimension to high speed and small form factor, and have been game changers for the industry. It is the package of the integrated circuit (IC) which holds the footprint to the printed circuit board (PCB), and thus it is the IC package which has enabled the multitude of small, handheld electronics to be invented and proliferate in today's world.

It is not just small size, but the added performance with high speed, more functionality, and the ability for handheld electronics to communicate via the Internet so that anyone with a smart phone or tablet has a wealth of information at their fingertips.

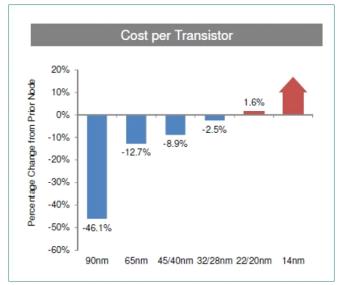

The costs per transistor is now going up with advancing technology nodes of 22nm and 14nm (see figure below), when traditionally the cost goes down. Increasingly the backend, or IC packaging, is being looked at a meeting the needs of tomorrow's technology demands rather than the front end manufacturing.

Courtesy of Amkor Technology and IEEE/CPMT

Chapter 3, Stacked Packages, explains the basics of this critical packaging technology, along with coverage of the latest products. Forecasts include units, prices, packaging revenue, package types, device types, first-level interconnection, and applications.

Chapter 4: Through Silicon Vias, 3-D and 2.5-D Integration is covered in depth, including 2.5-D interposer technology, with coverage of the latest new products and processes. Unit projections of both 2.5-D and 3-D are forecast, as are the identified potential markets for these technologies and their sizes, and 2.5-D interposer technology.

Chapter 5: System in Package (SiP) Solutions presents this package solution which combines an IC and passive devices in a single functional block, with a JEDEC footprint. New product introductions are presented. Forecasts include units, prices, packaging revenue, device types, interconnection, and applications.

The Multi-Component IC Packaging Market - 2014 Edition sells for \$1495 as a single-user license PDF file. Additional licenses sell for \$250 each and a corporate license sells for \$1000. With the purchase of the report, an Excel spreadsheet of all tables may be obtained for an additional \$750.

## **About the Author**

Sandra L Winkler has been an industry analyst starting in 1988, and from 1995 has been a staff member of Electronic Trend Publications, now New Venture Research Corporation. She has produced numerous off-the-shelf and custom reports throughout her career. She began her analyst career in the telecommunications industry, with Frost and Sullivan and since 1995 has focused on the semiconductor packaging industry, authoring more than 30 widely cited reports on the topic, most notably, The Worldwide IC Packaging Market, Advanced IC Packaging Markets and Trends, and IC Packaging Materials. She is a contributing editor and writer for Chip Scale Review magazine, Global SMT & Packaging News, and contributes to the IEEE/CPMT newsletter and other media. Ms. Winkler has earned an MBA from Santa Clara University and is on the executive planning committee of the IEEE/CPMT Santa Clara Valley chapter, serving as Luncheon Program Chair.

# The Multi-Component IC Packaging Market, 2014 Edition

## **Table of Contents**

## **Chapter 1: Introduction**

- 1.1 Background

- 1.2 Scope

- 1.3 Organization

- 1.4 Methodology

## **Chapter 2: Executive Summary**

- 2.1 Overview

- 2.2 Stacked Packages

- 2.3 Through-Vias Technology, 2-5D, and 3-D Interconnection Solutions

- 2.4 System in Package

## **Chapter 3: Stacked Packages**

- 3.1 Overview

- 3.2 Types of Stacked Packages

- Die stack

- PoP

- PiP

- Other

- 3.3 The Ins and Outs of Stacked Packages

- 3.4 Interconnection

- 3.5 Stacked Package as a Multi-Component Package

- 3.6 Wafer Thinning

- 3.7 End Markets and Application Trends

- 3.8 New Product Introductions

- 3.9 Unit and Revenue Forecasts

- Stacked Packages by Application

- End Markets for Stacked Packages

- Stacked Packages by Device Type

- Stacked Packages by Interconnection

## Chapter 4: Through Vias, 3-D and 2.5-D

## Integration

- 4.1 Through Vias and 3-D Overview

- 4.2 2.5-D

- 4.3 2.5-D Interposers and Microbumps

- 4.4 Wide I/O

- 4.5 Creating the Vias

- 4.6 Who Takes Ownership of each Process Steps?

- 4.7 What does it Cost to Create 2.5-D and 3-D Devices

- 4.8 Issues / Solutions / Call to Action

- 4.9 3-D Die-Stacking Technology Requirements

- 4.10 Bonding Methods

- 4.11 Via First, Middle, or Last Technology

- 4.12 Via Etching and Filling

- 4.13 New Product/Process Highlights

- **4.14 Industry Consortiums**

- 4.15 Market Potential

- 4.16 Future Markets

- 4.17 TSV Forecasts (2.5-D, 3-D, Interposer)

### **Chapter 5: System in Package**

- 5.1 Overview

- **5.2 Hybrid Memory Cube**

- **5.3 New Product**

Introductions/Highlights

- 5.5 SiP Forecasts

- Unit/Revenue Summary

- SiPs by Application

- SiPs by Device Type

- SiPs by Interconnection)

**Appendix A - Website Address Guide**

Appendix B - Glossary

# The Multi-Component IC Packaging Market, 2014 Edition

#### **List of Tables**

Table 3-1 Die Stack FBGA Package Solutions, 2011—2017 Table 4-16 Stacked Package Applications, 2011—2017 Table 3-2 Package-on-Package (PoP) Solutions, 2011—2017 Table 3-17 End-Product Markets Using Stacked Packages, Table 3-3 Package-in-Package (PiP) Solutions, 2011—2017 2011-2017 Table 3-4 Stacked TSOP Solutions, 2011—2017 Table 3-18 Stacked Packages Applications, 2011—2017 Table 3-5 Stacked QFN/QFP Solutions, 2011—2017 Table 3-19 Interconnection of Stacked Packages, 2001—2017 Table 3-6 Stacked MCM Solutions, 2011—2017 Table 4-1 General Features of Le'ti Interposer Table 3-7 Stacked WLP Solutions, 2011—2017 Table 4-2 General Features of a Multipurpose Interposer Table 3-8 Other Stacked Package Solutions, 2011—2017 Table 4-3 TSV Potential Markets, 2012–2017 Table 3-9 Summary Stacked Package Units, 2011—2017 Table 4-4 TSV Potential Market Revenue, 2012—2017 Table 3-10 Summary Stacked Package Assembly Revenue, Table 4-5 2.5-D and 3-D Forecast by Package Type, 2012—2017 2011—2017 Table 4-6 2.5-D and 3-D Forecast, 2012—2017 Table 3-11 Total ICs in Stacked Packages, 2011—2017 Table 4-7 2.5-D Interposer Forecast, 2012—2017 Table 3-12 Stacked Packages as a Percentage of Total ICs, Table 5-1 SiPs, 2011—2017 Table 5-2 Embedded Actives and Passives within the Table 3-13 Stacked Package Assembly Revenue as a Substrate, 2011-2017 Percentage of Total Assembly Revenue, 2011—2017 Table 5-3 SiP Applications, 2011—2017 Table 3-14 Stacked Packages as a Percent of Total ICs by Table 5-4 Available Market for SiP Applications, 2012—2017 Package Family, 2011—2017 Table 5-5 SiPs by Device Type, 2011—2017 Table 3-15 Stacked Package Assembly Revenue as a Table 5-6 Interconnection of SiPs, 2011—2017

The newest packaging products and latest research for the following companies are interspersed throughout the report:

3D Glass Solutions

APSTL, Ilc

Auburn University

CEA-Leti

Cisco, Inc. and Amkor Technology

Corning, Inc.

Dow Chemical

EV Group

Fraunhofer Institute for Reliability and Microintegration

Fujikura Ltd. and FlipChip International, LLC

Innovative Micro Technology

Kyocera America

Percent of Total Revenue, 2011—2017

Nanyang Technology University

Sandia National Laboratories

SET North America and RTI International CMET

Shinko Electric Industries

STATS ChipPAC Ltd.

SUNY College, College of Nanoscale Science and

Engineering

SUSS MicroTec

Texas Instruments

Tohoku University

Triton Micro Technologies, Inc. and nMode Solutions

Unimicron Technology Corporation and ITRI

Published January 2014, 188+ Pages

| Order Form                                                                                                                                                      |                                                                |        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--------|

| Payment Method Check in the amount of \$ is enclosed. Invoice per P.O. # Please charge: Visa MasterCard American Express Card # Exp Name On Card Signature Date | Name Title Company Address City/State/Zip Telephone Fax E-mail |        |

| The Multi-Component IC Packaging Market, 2014 Edition - single user license (PDF)                                                                               |                                                                | \$1495 |

| Extra Licenses (\$250 each), Corporate License (\$1000)                                                                                                         |                                                                |        |

| Returns: No return privileges. International Orders: Must be prepaid, please contact us for payment arrangements.                                               | Excel Spreadsheet (\$750)                                      |        |

| New Venture Research                                                                                                                                            | Subtotal                                                       |        |

| 337 Clay St., Suite 101 Nevada City, CA 95959 Tel: (530) 265-2004 Fax: (530) 265-1998 www.newventureresearch.com; info@newventureresearch.com                   | All files are in PDF format only  TOTAL                        |        |